고정 헤더 영역

상세 컨텐츠

본문

현대의 반도체는 고집적화되어서

89mm2 면적에 43억여 개의 트랜지스터가 들어갑니다.

이렇게 작은 반도체를 제작하기 위해서는 엄청난 기술과 장비가 요구됩니다.

또한, 이러한 것을 설명하기 위해서는 그 양이 방대합니다.

따라서 각각의 8대 공정을 다루고 해당 공정을 활용하여 반도체를 제작하는것까지

총 9편으로 제작될 예정입니다.

우선, “반도체 8대 공정”이란 반도체를 제작하기 위해 활용되는

8가지 주요 공정을 의미합니다.

반도체의 공정은 다음과 같은 8개의 공정으로 구분된다.

그 공정은 웨이퍼 제조, 산화공정, 포토공정, 식각공정, 증착 & 이온주입공정, 금속배선공정, EDS공정, 패키징 공정입니다.

이번 포스팅에서는 웨이퍼제조에 대하여 먼저 알아보도록 하겠습니다.

1. 웨이퍼 제조

건물을 제작할 때 가장 먼저 기반을 다지듯, 반도체를 제작할 때도 기초 바닥이 필요합니다.

반도체의 기초 바닥은 웨이퍼(Wafer)라고 부르는 얇은 원판이며

매우 고순도의 Si로 구성되어 있습니다.

웨이퍼는 요소에 따라 여러 크기로 제작이 가능하다.

웨이퍼의 크기가 클수록 그 위에 제작 가능한 반도체 칩의 수가 증가하기 때문에 생산 효율이 늘어나게 됩니다.

생산 효율이 늘어나게 되면 한번의 공정에 많의 양의 반도체를 생산할 수 있고 생산 비용의 절감으로

다른 업체들보다 우수한 경쟁력을 가질 수 있습니다.

하지만 웨이퍼 크기를 바꾸면 관련 장비를 모두 바꿔야 하기 때문에

경쟁력만을 위해서 무한정으로 웨이퍼 크기를 늘리는것은 무리가 있습니다.

최근에는 8인치(200mm)와 12인치(300mm)를 주로 생산하고 있습니다.

그리고 미래에는 18인치(450mm)를 생산할 것이라 합니다.

이러한 웨이퍼는 [잉곳(Ingot) 만들기] – [잉곳 절단하기] – [표면 연마] – [세척 및 검사]

4단계를 통해 제작됩니다. 이제 과정 하나하나 살펴보겠습니다.

a) 잉곳(Ingot)만들기

잉곳(Ingot)이라고 하는 것은 원통 모형으로 생긴 고순도 단결정 실리콘입니다.

이때 제작하는 ‘잉곳의 지름 = 웨이퍼의 지름’이게 됩니다.

그리고 말하는 ‘고순도’는 우리가 일반적인 범위를 뛰어넘습니다.

반도체업계에서는 순도에 대한 이야기를 할 때, ‘9나인’, ‘11나인’이라는 말을 사용합니다.

(일반적으로 'nine nine', 'eleven nine'이라고 읽습니다.)

해당 용어의 의미는 소수점 뒤에 9가 9개, 9가 11개 있다는 의미로 각각

9나인: 순도 99.999999999%

11나인: 순도 99.99999999999%

라는 수치를 가지고 있습니다.

해당 잉곳은 주로 쵸크랄스키 공법(Czochralski, CZ 공법)에 의해 만들어집니다.

CZ 공법은 ‘다결정 실리콘’을 고열로 녹여 액체 상태로 만든 단결정 실리콘(seed)을 접속한 후 천천히 회전하여 들어 올리면서 실리콘을 성장시키는 방법입니다.

해당 공법은 고체 실리콘(seed)과 액체 실리콘(액화된 다결정 실리콘) 사이의 접촉면에서 냉각이 발생하여 액체 실리콘이 seed에 맞춰서 결정 방향이 재구성되어 단결정 구조로 이어지게 됩니다.

이에 따라 seed가 점점 성장하게 되는 원리입니다.

(잉곳이 원통인 이유도 여기에 있습니다. 회전하는 방향이 원형임으로 결정도 원형으로 성장하기 때문입니다.)

CZ공법은 다음과 같은 순서로 이루어집니다.

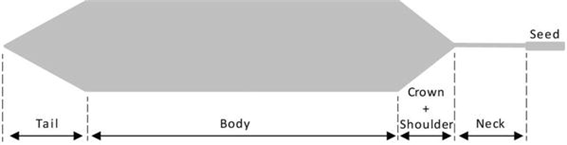

이렇게 생성된 ingot은 부위별로 사진과 같이 명칭이 정해지게 됩니다. 여기서 Body만 추출해서 웨이퍼로 활용하게 됩니다. (나머지 부위는 다시 녹여 새로운 잉곳을 만드는데 활용합니다.)

잉곳은 8개의 명칭이 있으며 Shoulder + Crown 부분에서는 꺾여진 부분만 Shoulder, 나머지를 Crown 이라고 한다.

각기 다른 크기의 웨이퍼를 생산하기 위해서는 잉곳의 두께(Body)를 다르게 생산해야 합니다.

이는 온도구배(고체~액체의 온도 차이), 인발 속도(들어올리는 속도),

회전 속도를 정밀하게 제어함으로 가능합니다.

『윗 문단에서 “다결정 실리콘”이라는 단어가 있었습니다.

잉곳의 원료가 되는 다결정 실리콘은 무엇일까요?

네이버나 구글에 검색하면 잉곳을 만드는 대표적인 다결정 실리콘 원료로 이산화규소(SiO2: 모래)가 나옵니다. 하지만 모든 모래가 이산화규소도 아닐뿐더러 불순물이 많아 고순도 작업에 어려움이 있을 것 같습니다.

이론적으로는 모래가 맞지만, 많은 기업에서는 모래 대신 폴리실리콘(PolySilicon)을 사용합니다. 폴리실리콘은 말 그대로 다결정(Poly:다수, 많은) 실리콘(Si)라는 의미입니다.

모래가 반도체의 원료라고 알고 있지만, 대부분 폴리실리콘을 사용한다.

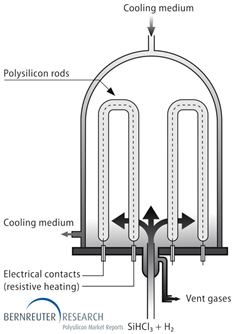

(반도체용)폴리실리콘을 만드는 방법은 지멘스(Siemens) 공법과

FBR(Fluidised Bed Reactor) 공법 2가지가 있습니다.

지멘스 공법은 ‘*코크스’를 도가니에 넣고 가열하여 고리 모양(Rod) 금속급 실리콘(MG-Si)를 생산한 후, 해당 금속급 실리콘을 가열로에 넣고 실란가스(실리콘 가스: 삼연화실란, 모노실란 등)와 화학적으로 반응시켜 정제된 폴리실리콘을 만들어냅니다.

[흔히 CVD(Chemical Vapor Deposition) 공법으로 실리콘을 성장시키는 방법이라고 합니다.]

*‘코크스’는 석탄(점결탄)을 건류(도가니에서 공기를 차단하고 가열)하여 제작합니다.

지멘스 공법은 CVD를 이용하는 공법이다.

이러한 공법은 금속급 실리콘을 1,100℃로 상시 유지해야기 때문에 전기사용량이 많고 실란 가스 활용과 유출 방지를 위한 대규모 설비투자가 필요하며 생산속도가 느리다는 단점이 있습니다. 하지만 1950년대부터 활용되어 안정적인 기술이기 때문에 90%이상의 폴리실리콘 업체가 사용하는 공법입니다.

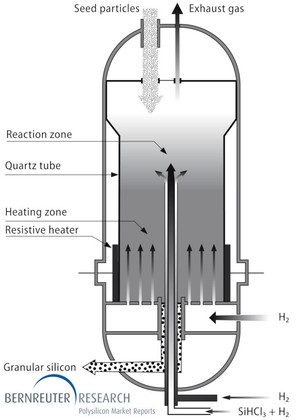

FBR공법은 수소가스가 채워진 도가니에 실리콘 입자(Seed)를 투입하고, 실란가스를 주입하여 실리콘 입자를 낙하시켜 지름 1cm의 구형 실리콘을 생성하는 공법입니다.

FBR를 주요 공법으로 쓰기에는 많은 연구가 필요하다.

해당 공법은 지멘스 공법보다 전력 소비가 적고, 생산 속도도 빠르지만, 실리콘 입자의 낙하 과정에서 불순물 오염 가능성이 커서 수율이 낮은 편입니다.』

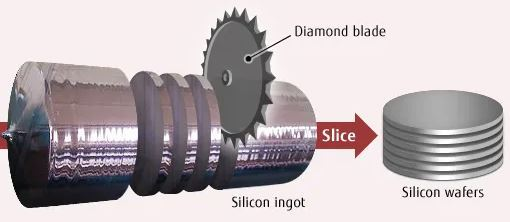

b. 잉곳 절단하기

위의 방식대로 만들어진 잉곳은 공법의 한계로 인해 완전한 원통형이 아니며 아래와 위쪽에 원뿔의 형태를 합친 모양입니다. 따라서 우리가 원하는 웨이퍼의 모양을 만들기 위해서는 잉곳을 절단하게 됩니다.

사진 설명을 입력하세요.

잉곳을 절단할 때는 공업용 다이아몬드 톱을 이용하여 균일한 두께로 써는 것이 중요합니다.

그 두께는 SEMI(Semiconductor Equipment and Material Institute: 반도체 제조 장비 재료 협회)의 기준에

따라 8인치에서는 0.725mm, 12인치에서는 0.775mm (두께 오차 ±0.025 mm)로 하는 것이 일반적입니다.

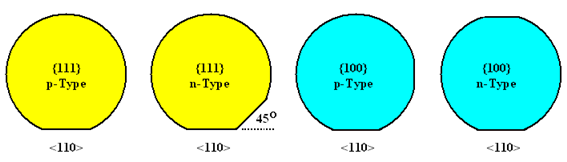

웨이퍼는 단결정인 만큼 그 결정 방향도 중요합니다. 하지만 결정 방향은 맨눈으로 알 수 없으므로 사전에 잉곳의 결정 방향을 파악하고 육안으로 쉽게 알아볼수 있게 표시를 하게 됩니다.

웨이퍼의 type과 결정방향에 따라 눈으로 구분하기 쉽게 표기한다.

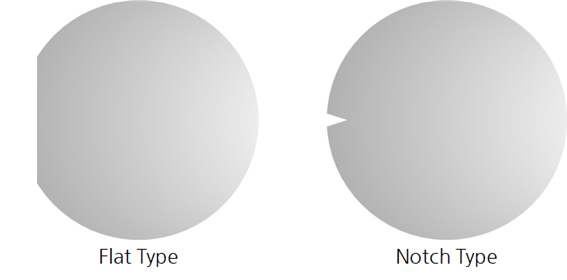

그 표시가 바로 플랫존(Flat Zone)과 노치(Notch)입니다.

플랫존은 웨이퍼의 결정 방향에 따라 정해진 기준대로 원 한쪽을 평평하게(Flat) 자르는 것입니다.

노치는 웨이퍼의 결정 방향에 따라 한쪽을 움푹하게 만들어 표시하게 됩니다.

Flat과 Notch의 방향은 같다.

플랫존과 노치의 기존은 같으며 최근에는 웨이퍼 훼손량이 적은 노치를 선호한다고 합니다.

c. 표면 연마

흔히 반도체 공정을 건물 세우는 것에 비유하는 경우가 있습니다. 지반을 다지고 건물을 설계대로 층을 높혀가는 과정이 반도체 공정과 비슷하기 때문인 것 같습니다.

이번 ‘표면 연마’ 공정을 건물에 비유하면 ‘지반 다지기’와 같습니다.

건물을 짓는데 바닥이 평평하지 않으면 층을 올릴수록 기울어지게 되고 끝내 무너지게 됩니다.

반도체도 마찬가지입니다.

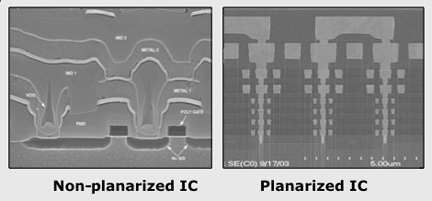

특히 현재의 반도체는 고도의 소형화, 미세화, 정밀화가 진행되고 있어서 조그마한 단차라도 있으면

해당 제품은 불량이 됩니다.

(왼쪽)표면 연마를 거치지 않은 IC (오른쪽)표면 연마를 거친 IC

따라서 일반적인 연마작업(Polishing)이 아닌

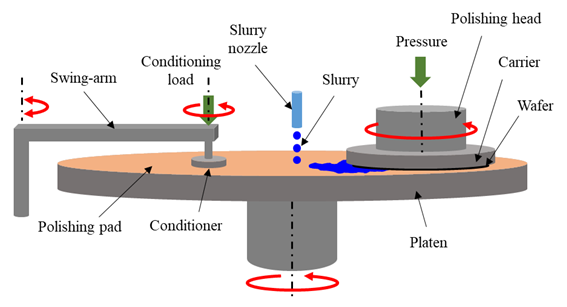

CMP(Chemical Mechanical Polishing: 화학적 기계적 연마)를 하게 됩니다.

CMP는 테이블 위에 여러 개의 Pad(폴리 우레탄)를 고정하고, Pad 위에 웨이퍼를 밀착시킨 상태에서 수백 nm의 연마제가 들어있는 슬러리(Slurry)를 분산되게 합니다. 그

리고 해당 Pressure head로 웨이퍼에 압력을 가하고 pad를 고속 회전시켜 평탄화를 진행하는 방법입니다.

반도체의 소형화가 주목받는 지금, CMP는 가장 주목받는 공법이 되었다.

이러한 이유로 CMP공정에서 Pad의 회전 속도, 슬러리의 농도, Head의 압력이

웨이퍼의 평탄화 품질을 결정하는 가장 중요한 요소가 됩니다.

해당 방법을 ‘화학적. 기계적’ 연마라고 부르는 이유는 pad를 고속 회전하게 되면 상대적으로 높은 부위가 높은 압력을 받아 먼저 갈리면서 기계적으로 평탄화 진행이 되고,

슬러리를 통해 기계적 마찰로 발생하는 여러 문제(스크래치 등)를 완화하고

화학적 작용으로 물질 종류에 따라 선택적 연마가 가능하기 때문입니다.

[이에 대한 자세한 내용은 3편인 <식각 공정>에서 다루도록 하겠습니다.]

CMP공정 중 마찰에 의한 기계적 연마를 진행하게 되는데 이때 마찰열이 발생하게 됩니다.

마찰열이 발생하게 되면 Pad가 녹아 웨이퍼에 손상을 줄 수 있을 뿐만 아니라 웨이퍼의 단결정 상태가 무너져 결함이 발생할 수 있습니다. 따라서 열을 식히기 위해 물을 지속하여 투입하게 됩니다.

반도체 공정에서 사용하는 물은 일반적인 물이 아닙니다.

우리가 사용하는 물에는 많은 불순물과 화학물질이 섞여 있어서 보통의 물을 투입하면 wafer를 훼손하게 됩니다. 이러한 이유로 아무것도 없는 순수(純水, Deionized water: D.I water)를 사용하게 됩니다.

사진 설명을 입력하세요.

순수에 대한 부분은 [세척 및 검사]에서 자세히 다루도록 하겠습니다.

d. 세척 및 검사

잘 다듬어진 웨이퍼는 잔류 슬러리와 웨이퍼 가루를 닦아내기 위해서 세척을 진행합니다.

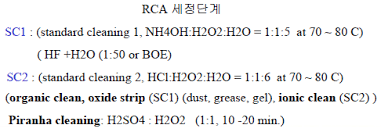

이때, 다른 화학적 반응을 방지하고자 RCA공정을 통해 세척하게 됩니다.

RCA공정은 일반적으로 표준세정-1(SC-1; standard cleaning 1)과

표준세정-2(SC-2; standard cleaning 2)로 구분됩니다. 각 세정단계를 자세히 살펴보겠습니다.

RCA세정 단계는 2단계로 구분된다.

먼저, SC-1은 NH4OH(29% 수용액) : H2O2(30% 수용액): D.I water = 1:5:1(부피비)의 혼합물 속에서 5분 동안 끓인 후(70℃), 차가운 D.I water에서 헹구는 과정입니다.

이러한 과정을 통해 강한 산화작용을 발생시켜 유기물질의 산화 및 용해와 잔류 금속 불순물을 제거하게 됩니다.

다음의 SC-2 는 HCl(37% 수용액): H2O2(30% 수용액): D.I water = 1:1:6(부피비)의 혼합물 속에서 5~10분간 끓인 후(70℃), 차가운 D.I water에서 헹구는 과정입니다.

이 과정에서 알칼리 이온과 물에 녹지 않는 수산화 물질, 잔류하는 불순물이 모두 제거됩니다.

『산업 현장에서 사용하는 순수(純水, D.I water)의 기준은 25℃에서 비저항이 18MΩ·cm로 거의 전기가 통하지 않아야 합니다. 하지만 최근 반도체가 초미세화되면서 1.8MΩ·cm정도의 초순수를 사용한다고 합니다.

이러한 순수는 다양한 방법을 거쳐 생산합니다. 그 방법이 복잡하나,

간략히 설명하자면 크게 역침투법과 임계여과법을 아래와 같은 순서로 조합하는 방식입니다.

물> 전처리> 역침투막> 진공탈기> 이온교환> 진공탈기> 이온교환> UV 살균> 이온교환> 역침투막> 순수(純水)

역침투막: 구멍의 크기가 2nm보다 작은 여과막(Reverse Omosis membrane:RO막)을 이용하여 미립자를 거르는 과정

진공탈기: 물을 고진공상태에 두어서 물 내부에 있는 기체를 제거하는 과정

이온교환: 레진(Resin)에 물을 통과시켜 중금속 이온을 제거하는 과정

UV 살균: 물 내부의 유기물을 산화, 분해하는 과정.』

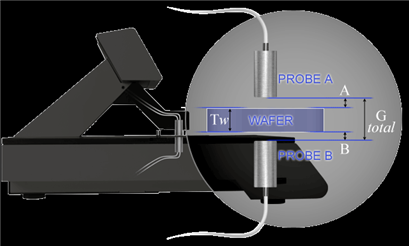

세척된 웨이퍼는 기기들을 거쳐 순도와 지름, 두께 등이 일정한지 검사하고 통에 넣어져

다음 단계인 회로를 새기는 단계로 넘어가게 됩니다.

wafer를 검사할때는 주로 probe를 이용한다.

이렇게 만들어진 아무것도 없는 웨이퍼를 ‘베어 웨이퍼(Bare wafer)’라고 합니다.

우리가 아는 SK하이닉스와 삼성전자는 Bare wafer를 외부에서 구매해서 사용합니다.

이런 베어 웨이퍼를 생산하는 업체에서는

센서와 메모리 반도체 제작을 위한 Polished wafer(Bare wafer)

비메모리 반도체 제작을 위한 Epitaxial wafer(Bare wafer 위에 결정 방향대로 실리콘을 얇게 성장시킨 것) 2가지의 웨이퍼를 생산합니다.

SK 실크론에서 제작하는 wafer (왼쪽) Polished wafer (오른쪽) Epitaxial wafer

이러한 웨이퍼 제작만을 전문으로 하는 대표적인 업체로는 “SK 실크론”이 있습니다.

끝!

<사진 및 자료 출처>

1. 8대 공정 사진: https://kimdoil.tistory.com/39

2. 웨이퍼 사진: https://semiengineering.com/inspecting-unpatterned-wafers/

3. 잉곳 영역 네이밍 사진: https://www.intechopen.com/chapters/55116

4. CZ공법 사진:https://www.sciencedirect.com/topics/chemistry/czochralski-process

5. 폴리실리콘 사진: https://m.post.naver.com/viewer/postView.nhn?volumeNo=17186984&memberNo=5673438

6. 지메스 공법 사진: https://www.bernreuter.com/polysilicon/production-processes/

7. FRB 공법 사진: https://www.bernreuter.com/polysilicon/production-processes/

8. wafer sawing 사진: https://yeonidoggi.tistory.com/64

9. flat & notch 사진: https://e-funny.tistory.com/97

10. 결정방향별 flat 위치 사진: https://www.tf.uni-kiel.de/matwis/amat/elmat_en/kap_5/illustr/i5_2_4.html

11. CMP전 & 후 비교 사진: http://www.linx-consulting.com/Specialty-abrasives-CMP.html

12. CMP 장비 구성 요소 사진: https://www.mdpi.com/2076-3417/11/8/3521/htm

13. 물 사진: https://www.nihon-trim.co.jp/media/19209/

14. RCA세정 자료: https://m.blog.naver.com/PostView.naver?isHttpsRedirect=true&blogId=klp0712&logNo=221089028397

15. 웨이퍼 검사 장비 사진: http://ko.dsnsolar.com/info/wafer-bow-warp-thickness-measurement-for-metro-43550039.html

16. Polished Wafer & Epitaxial Wafer 사진: https://www.sksiltron.com/m/ko/wafer/wafer.do

<도움이 많이 된 사이트>

이전 포스팅에서 격자구조, 그 중에서 다이아몬드 격자구조에 대해 자세히 다뤘다. 하나의 Si atom이 인접한 4개의 Si atom과 똑같은 크기와 각도를 갖고 3차원적으로 공유 결합을 한다는 것이었고, 그리는 방법까..

hy-kong.tistory.com

'프로젝트 > 반도체 공정' 카테고리의 다른 글

| 반도체 제작과정③_반도체 8대 공정(Photo공정) : Before Photo (1) | 2023.12.06 |

|---|---|

| 반도체 제작과정③_반도체 8대 공정(Photo공정) : Before Photo (0) | 2023.12.06 |

| 반도체 제작과정②_반도체 8대 공정(산화공정) (3) | 2023.12.06 |